BoxLambda, a retro-style FPGA based computer project using VERA

-

epsilon537

- Posts: 31

- Joined: Sun May 01, 2022 12:12 pm

BoxLambda, a retro-style FPGA based computer project using VERA

I pushed a new post, discussing BoxLambda's architecture, including an actual Block Diagram! ?

https://epsilon537.github.io/boxlambda/architecture-first-draft/

-

epsilon537

- Posts: 31

- Joined: Sun May 01, 2022 12:12 pm

BoxLambda, a retro-style FPGA based computer project using VERA

A new post in the BoxLambda project Blog, about interrupts and FPGA resource utilization:

https://epsilon537.github.io/boxlambda/interrupts-and-fpga-utilization/

BoxLambda, a retro-style FPGA based computer project using VERA

It looks like you can either take two clock cycles to use the DMA to use the Dual-Port RAM as audio buffer, or else use the DMA or the CPU to take four cycles (at least) to use the DDR2 as sound RAM, which may be necessary if you've exceeded your total sprite, or scanline limit, and wanted to add in some BOBs as extra enemies, bullets, fireballs, or clouds in your vertical-scrolling shoot-'em-up, or bit-bang in more parallax scrolling fields?

Question No. 1: While it doesn't look like it will happen in hardware, do you plan to designate specific stretches of Dual Port and/or DDR2 as sound buffer? Or will programmers have to be doubly careful about reads and writes to prevent the use of sound data as general logic code, or the YM2149s from reading data meant for A.I. routines and spitting out garbage from the speakers.

Question No. 2: Do you believe you have enough fabric RAM to stick a YM2151 on the Nexys A7-100T?

-

epsilon537

- Posts: 31

- Joined: Sun May 01, 2022 12:12 pm

BoxLambda, a retro-style FPGA based computer project using VERA

On 6/1/2022 at 2:22 AM, Kalvan said:

It looks like you can either take two clock cycles to use the DMA to use the Dual-Port RAM as audio buffer, or else use the DMA or the CPU to take four cycles (at least) to use the DDR2 as sound RAM, which may be necessary if you've exceeded your total sprite, or scanline limit, and wanted to add in some BOBs as extra enemies, bullets, fireballs, or clouds in your vertical-scrolling shoot-'em-up, or bit-bang in more parallax scrolling fields?

Question No. 1: While it doesn't look like it will happen in hardware, do you plan to designate specific stretches of Dual Port and/or DDR2 as sound buffer? Or will programmers have to be doubly careful about reads and writes to prevent the use of sound data as general logic code, or the YM2149s from reading data meant for A.I. routines and spitting out garbage from the speakers.

Question No. 2: Do you believe you have enough fabric RAM to stick a YM2151 on the Nexys A7-100T?

I haven't worked out the cycle counts. A small part of the DPRAM, or even Praxos internal memory might be set up as audio buffer if needed. The VERA already has an audio buffer, however. YM2149 register access should be at a low enough rate, buffering might not be needed.

The audio is usually not competing with graphics for bandwidth. All graphics resources reside in VRAM, not DDR or DPRAM. Although I can imagine in some cases we might be loading new graphics resources from DDR into VRAM on-the-fly, i.e. a kind of VRAM banking mechanism. If there is concurrent access from the CPU and DMA to DDR, they will be serviced in a round-robin schedule, so each can account on 50% of the bandwidth.

Q1: in HW, no. No MPU or MMU. The programmer will have to be careful. I don't intend to implement any mechanisms to prevent people from shooting themselves in the foot.

Q2: on the Nexys A7-100T, easily. On the Arty A7-35T, probably not, although maybe the dual YM2149s can be traded for a single YM2151. I would have to synthesize the YM2151 to see how the numbers work out.

-

epsilon537

- Posts: 31

- Joined: Sun May 01, 2022 12:12 pm

BoxLambda, a retro-style FPGA based computer project using VERA

A new post in the BoxLambda project Blog, about the git workflow I'll be using, and my setup:

https://epsilon537.github.io/boxlambda/git-workflow-and-setup/

-

epsilon537

- Posts: 31

- Joined: Sun May 01, 2022 12:12 pm

BoxLambda, a retro-style FPGA based computer project using VERA

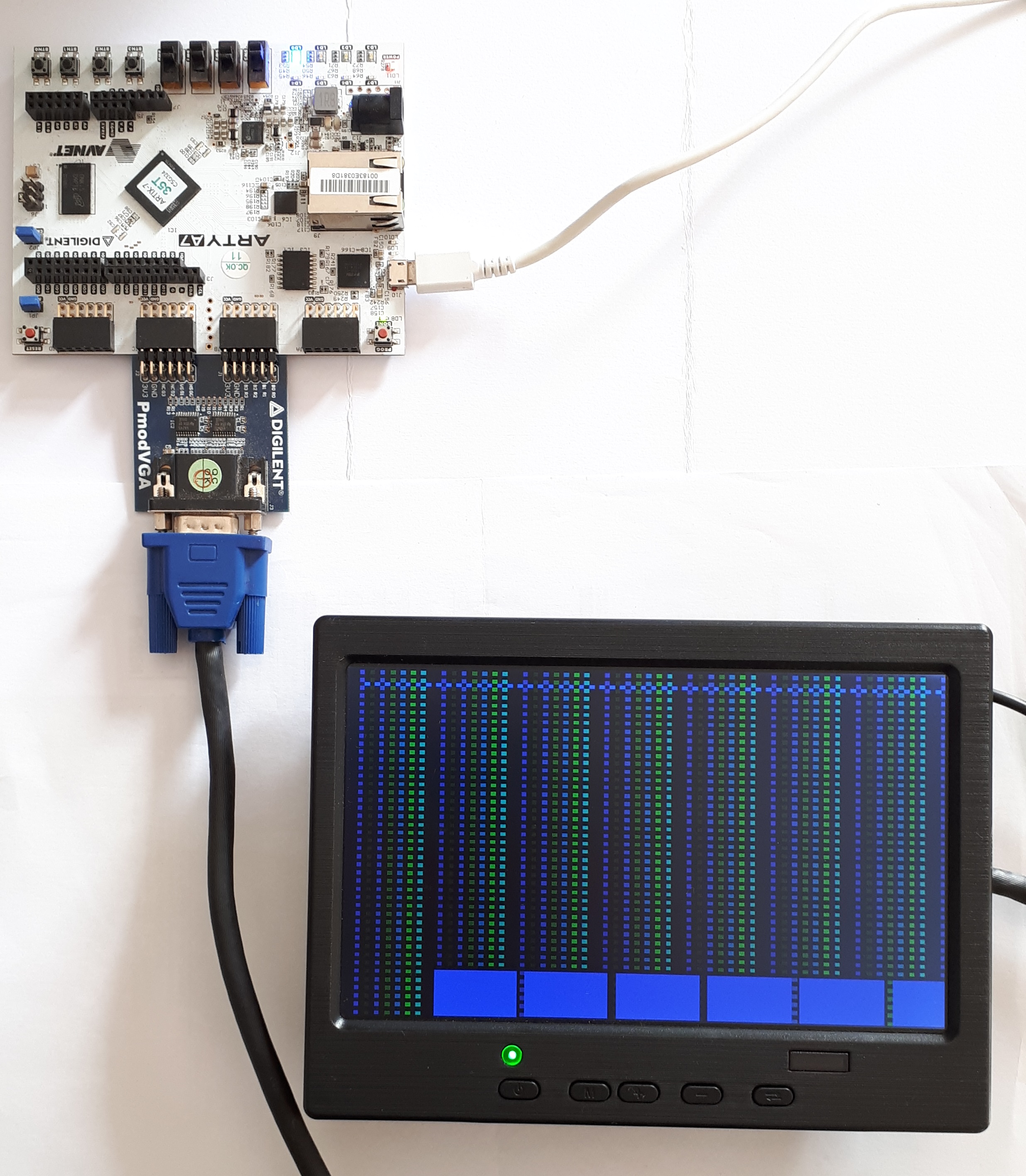

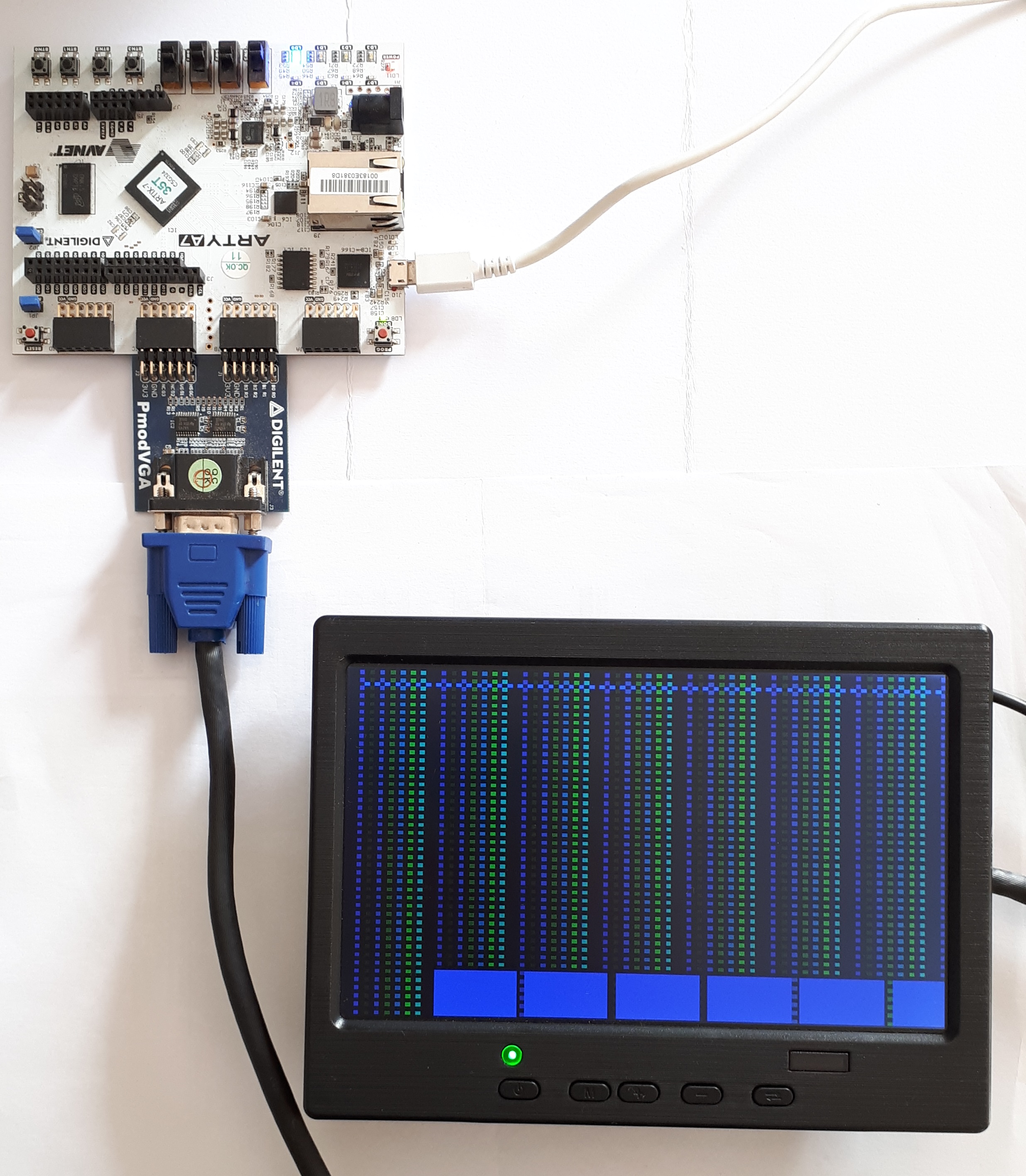

Another post in the BoxLambda Blog. I'm building a tiny bootstrap version of the system and bring it up on my Arty A7-35T:

https://epsilon537.github.io/boxlambda/hello-world/

-

epsilon537

- Posts: 31

- Joined: Sun May 01, 2022 12:12 pm

BoxLambda, a retro-style FPGA based computer project using VERA

I've been working on a build system for BoxLambda:

https://epsilon537.github.io/boxlambda/make-and-bender/

-

epsilon537

- Posts: 31

- Joined: Sun May 01, 2022 12:12 pm

BoxLambda, a retro-style FPGA based computer project using VERA

Two BoxLambda devlog posts for the price of none:

Testing with Verilator

Warnings and Verilator Lint

-

epsilon537

- Posts: 31

- Joined: Sun May 01, 2022 12:12 pm

Re: BoxLambda, a retro-style FPGA based computer project using VERA

I integrated the VERA Versatile Embedded Retro Adapter into the BoxLambda SoC. The Blog post below discusses the changes I made to the VERA core to interface it with a 32-bit system.

https://epsilon537.github.io/boxlambda/ ... ting-vera/

https://epsilon537.github.io/boxlambda/ ... ting-vera/